El diseño inverso de chips, en términos simples, es el proceso de extracción, análisis y organización de los circuitos internos de un chip para lograr una comprensión profunda de los principios técnicos, ideas de diseño, procesos de fabricación, mecanismos estructurales y otros aspectos del chip. Se puede utilizar para verificar marcos de diseño o analizar problemas de flujo de información en tecnología, y también puede ayudar en nuevas soluciones de diseño de chips o productos.

Tecnología Sichi Ha estado comprometida durante mucho tiempo a proporcionar soporte técnico y servicios para empresas de diseño en posicionamiento de productos, investigación y análisis competitivos, protección de derechos de autor y aprendizaje de conceptos y habilidades de diseño avanzado a través de la cooperación con empresas de diseño de chips conocidas. Tenemos nuestras propias habilidades técnicas y prácticas únicas en diseño inverso de chips. Nuestra extracción inversa de circuitos rápida y precisa, así como la colación y el análisis eficiente de circuitos, pueden proporcionar a los clientes con una plataforma de innovación independiente, acortando así la curva de aprendizaje y acelerando la mejora de su propio nivel técnico.

|

Circuitos Digitales |

Circuitos analógicos |

Alcance del Servicio de Diseño |

Celdas estándar, matrices de puertas, diseños semi-personalizados y completamente personalizados |

Proceso CMOS y proceso bi-poly |

Contenido del servicio |

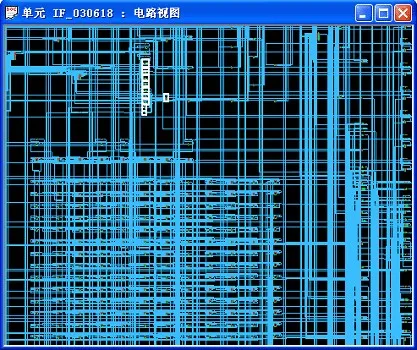

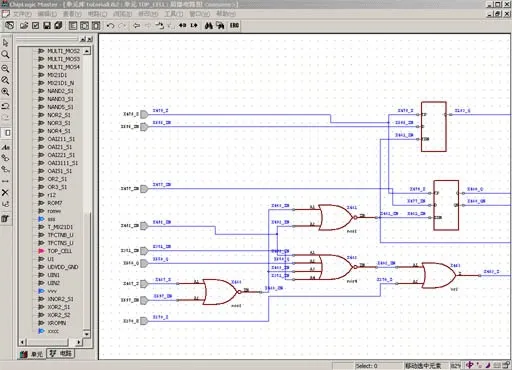

Proporcione esquemas de circuito de dos niveles (nivel superior y nivel de celda / nivel de puerta) como se muestra en la figura a continuación. Los esquemas de circuito se pueden generar de acuerdo con la ubicación del diseño; proporcionar verificación de ERC y admitir flujo SVS. |

Proporcionar listas de red / esquemas de circuitos a nivel de transistores, incluidos parámetros geométricos como la relación ancho / longitud del transistor; generar esquemas de circuitos según la ubicación del diseño; proporcionar verificación de ERC y admitir flujo SVS. |

Entrega De Datos |

Formatos de datos: Verilog y EDIFEntregables: Datos de imagen, datos de netlist en bruto y esquemas de circuito de dos niveles generados en función de las posiciones de diseño. |

Formatos de datos: SPICE y EDIFEntregables: Datos de imagen, datos de netlist en bruto y esquemas de circuito generados en función de las posiciones de diseño. |

Nuestros servicios de diseño inverso de chip incluyen extracción inversa esquemática de netlist / circuito, colación de circuitos jerárquicos, análisis de funciones lógicas, extracción y diseño de diseño, verificación y ajuste de reglas de diseño, verificación de diseño lógico, reemplazo de biblioteca de celdas y escalado de tamaño de proceso.

A través de estos métodos de análisis inverso, podemos ayudar a los clientes a comprender el diseño de otros productos para estudios de viabilidad de proyectos, abrir ideas, identificar problemas, contabilidad de costos, etc. Por ejemplo, antes de entrar en un nuevo campo, podemos evaluar y verificar la viabilidad de nuestras soluciones técnicas e ideas de diseño; Ayudar a resolver problemas técnicos críticos a través de la investigación sobre productos maduros en el mercado; Utilizar los recursos de mercado de los productos existentes, reducir las barreras de entrada, lograr una mejor compatibilidad de productos, etc.

Extracción inversa de netlist / diagrama de circuito

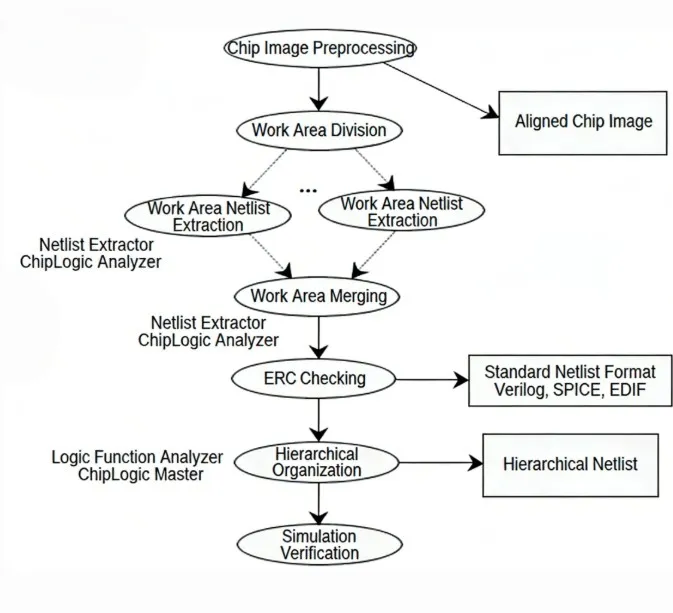

En el diseño inverso de chips, la extracción de netlist / diagramas de circuitos es un problema importante, y la calidad y velocidad de extracción de netlist afectan directamente a la organización posterior, simulación, LVS y otros aspectos del trabajo. Basado en resumir numerosos casos exitosos y confiando en aplicaciones de software desarrolladas independientemente, podemos extraer netlist / diagramas de circuitos con precisión, rapidez y con alta calidad.

Proceso estándar para la extracción de netlist y el análisis funcional

Análisis De Funciones Lógicas

Después de que se completa la extracción del netlist, a menudo es necesario organizar el circuito hibernando un circuito aplanado para formar una estructura jerárquica del circuito, para comprender las ideas y técnicas de diseño del diseñador, y también para lograr el objetivo de encontrar errores de netlist.

Análisis De Funciones Lógicas 1

Análisis De Funciones Lógicas 2

Diseño de diseño

El diseño de diseño es la implementación física de la lógica de circuitos y es la implementación de productos de circuitos integrados (editor de capas ChipLogic). Brindamos varios servicios de diseño como extracción de diseño, reemplazo de biblioteca de procesos, modificación de proceso objetivo, inspección DRC y verificación LVS basada en diseño inverso. El contenido del servicio es el siguiente:

Alcance del Servicio de Diseño |

Circuito digital |

Circuito analógico |

Celda estándar, matriz de puertas, semi-personalizada y completamente personalizada |

Proceso COMS y Proceso TTL |

|

Contenido del servicio |

Extraiga diseños de nivel superior y de celda; Comprobación completa de DRC; Reemplazo de biblioteca de celdas y escalado de tamaño de proceso |

Extraer diseño de nivel superior; Verificación de reglas de diseño de DRC |

Entrega De Datos |

Formato de datos: GDSII; Proporcionar datos de imagen, datos de diseño originales y datos de diseño aprobados por DRC |

Formato de datos: GDSII; Proporcionar datos de imagen, datos de diseño originales y datos de diseño aprobados por DRC |

Proceso Estándar para la Extracción de Diseños y el Análisis Funcional

Verificación de diseño lógico

Después de completar el diseño de la lista de red y el diseño, a menudo se requieren varias verificaciones de su corrección. Para garantizar la integridad del proceso de diseño, Sichi Technology proporciona varios servicios de verificación para los datos de la lista de red de chips y los datos de diseño.

1 |

Verificación de la FPGA |

Verificar la corrección de la extracción lógica quemando el chip |

2 |

Verificación de simulación lógica |

Verificar la corrección de la extracción lógica escribiendo vectores de prueba de acuerdo con la especificación del chip proporcionada por el usuario. |

3 |

Verificación de LVS |

Verificar la consistencia entre el diseño y el esquema |